Jenis-jenis Gerbang Logika Dasar dan Simbolnya

Terdapat 7 jenis Gerbang Logika Dasar yang membentuk sebuah Sistem Elektronika Digital, yaitu :

- Gerbang AND

- Gerbang OR

- Gerbang NOT

- Gerbang NAND

- Gerbang NOR

- Gerbang X-OR (Exclusive OR)

- Gerbang X-NOR (Exlusive NOR)

Tabel yang berisikan kombinasi-kombinasi Variabel Input (Masukan) yang menghasilkan Output (Keluaran) Logis disebut dengan “Tabel Kebenaran” atau “Truth Table”.

Input dan Output pada Gerbang Logika hanya memiliki 2 level. Kedua Level tersebut pada umumnya dapat dilambangkan dengan :

- HIGH (tinggi) dan LOW (rendah)

- TRUE (benar) dan FALSE (salah)

- ON (Hidup) dan OFF (Mati)

- 1 dan 0

Contoh Penerapannya ke dalam Rangkaian Elektronika yang memakai Transistor TTL (Transistor-transistor Logic), maka 0V dalam Rangkaian akan diasumsikan sebagai “LOW” atau “0” sedangkan 5V akan diasumsikan sebagai “HIGH” atau “1”.

Berikut ini adalah Penjelasan singkat mengenai 7 jenis Gerbang Logika Dasar beserta Simbol dan Tabel Kebenarannya.

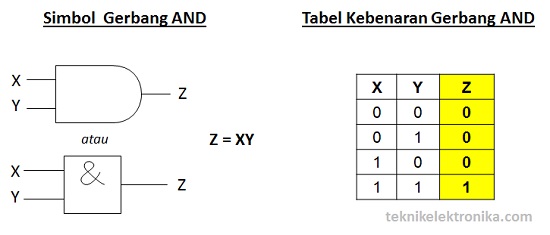

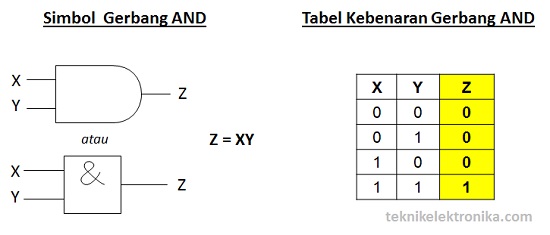

Gerbang AND (AND Gate)

Gerbang AND memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang AND akan menghasilkan Keluaran (Output) Logika 1 jika semua masukan (Input) bernilai Logika 1 dan akan menghasilkan Keluaran (Output) Logika 0 jika salah satu dari masukan (Input) bernilai Logika 0. Simbol yang menandakan Operasi Gerbang Logika AND adalah tanda titik (“.”) atau tidak memakai tanda sama sekali. Contohnya : Z = X.Y atau Z = XY.

Simbol dan Tabel Kebenaran Gerbang AND (AND Gate)

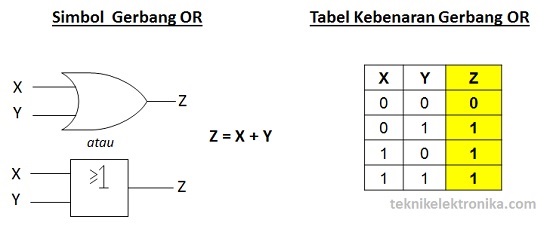

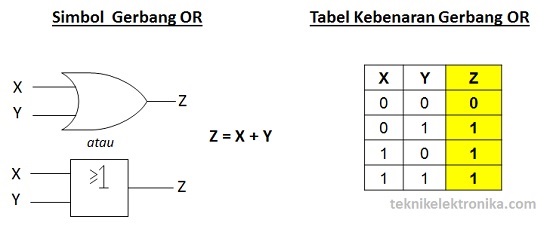

Gerbang OR (OR Gate)

Gerbang OR memerlukan 2 atau lebih Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang OR akan menghasilkan Keluaran (Output) 1 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin menghasilkan Keluaran (Output) Logika 0, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol yang menandakan Operasi Logika OR adalah tanda Plus (“+”). Contohnya : Z = X + Y.

Simbol dan Tabel Kebenaran Gerbang OR (OR Gate)

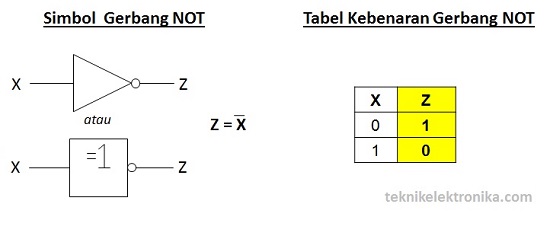

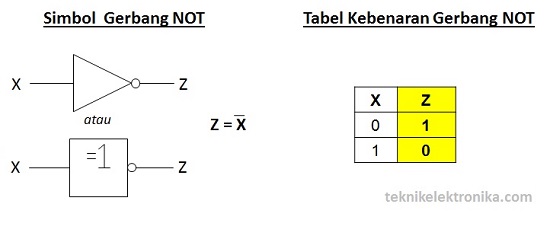

Gerbang NOT (NOT Gate)

Gerbang NOT hanya memerlukan sebuah Masukan (Input) untuk menghasilkan hanya 1 Keluaran (Output). Gerbang NOT disebut juga dengan Inverter (Pembalik) karena menghasilkan Keluaran (Output) yang berlawanan (kebalikan) dengan Masukan atau Inputnya. Berarti jika kita ingin mendapatkan Keluaran (Output) dengan nilai Logika 0 maka Input atau Masukannya harus bernilai Logika 1. Gerbang NOT biasanya dilambangkan dengan simbol minus (“-“) di atas Variabel Inputnya.

Simbol dan Tabel Kebenaran Gerbang NOT (NOT Gate)

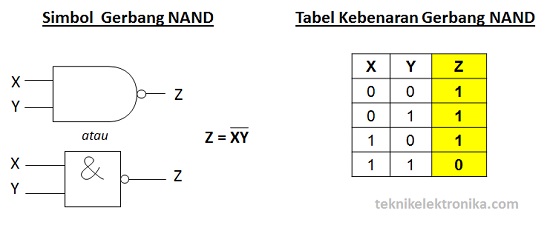

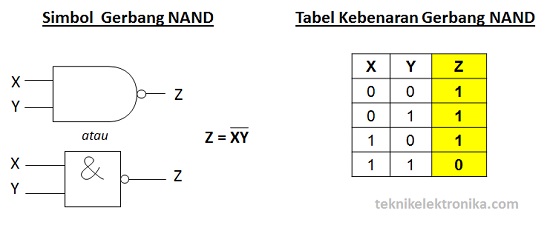

Gerbang NAND (NAND Gate)

Arti NAND adalah NOT AND atau BUKAN AND, Gerbang NAND merupakan kombinasi dari Gerbang AND dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang AND. Gerbang NAND akan menghasilkan Keluaran Logika 0 apabila semua Masukan (Input) pada Logika 1 dan jika terdapat sebuah Input yang bernilai Logika 0 maka akan menghasilkan Keluaran (Output) Logika 1.

Simbol dan Tabel Kebenaran Gerbang NAND (NAND Gate)

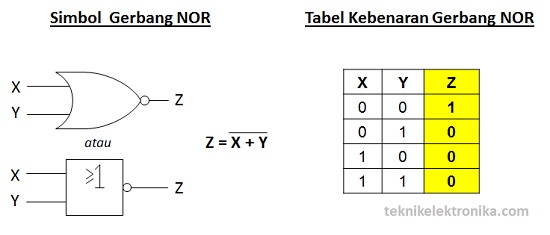

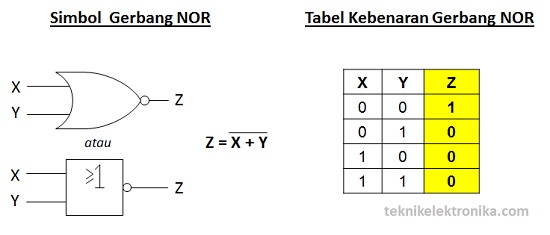

Gerbang NOR (NOR Gate)

Arti NOR adalah NOT OR atau BUKAN OR, Gerbang NOR merupakan kombinasi dari Gerbang OR dan Gerbang NOT yang menghasilkan kebalikan dari Keluaran (Output) Gerbang OR. Gerbang NOR akan menghasilkan Keluaran Logika 0 jika salah satu dari Masukan (Input) bernilai Logika 1 dan jika ingin mendapatkan Keluaran Logika 1, maka semua Masukan (Input) harus bernilai Logika 0.

Simbol dan Tabel Kebenaran Gerbang NOR (NOR Gate)

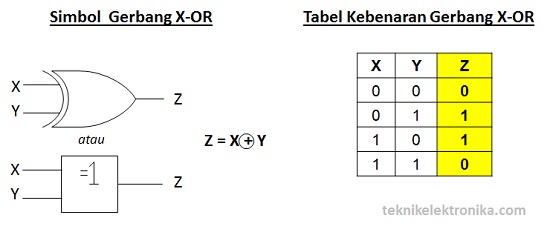

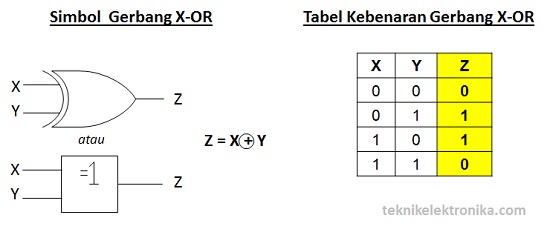

Gerbang X-OR (X-OR Gate)

X-OR adalah singkatan dari Exclusive OR yang terdiri dari 2 Masukan (Input) dan 1 Keluaran (Output) Logika. Gerbang X-OR akan menghasilkan Keluaran (Output) Logika 1 jika semua Masukan-masukannya (Input) mempunyai nilai Logika yang berbeda. Jika nilai Logika Inputnya sama, maka akan memberikan hasil Keluaran Logika 0.

Simbol dan Tabel Kebenaran Gerbang X-OR (X-OR Gate)

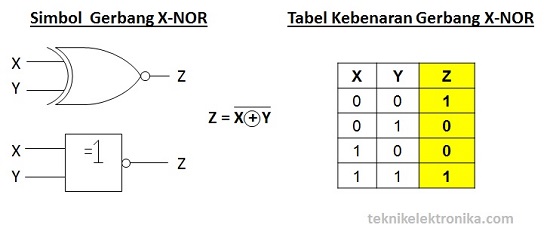

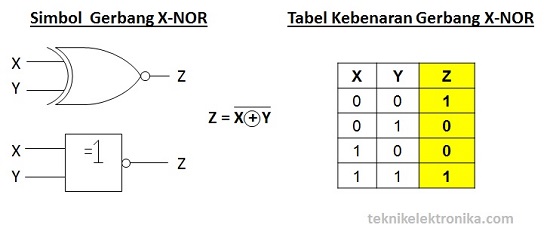

Gerbang X-NOR (X-NOR Gate)

Seperti Gerbang X-OR, Gerban X-NOR juga terdiri dari 2 Masukan (Input) dan 1 Keluaran (Output). X-NOR adalah singkatan dari Exclusive NOR dan merupakan kombinasi dari Gerbang X-OR dan Gerbang NOT. Gerbang X-NOR akan menghasilkan Keluaran (Output) Logika 1 jika semua Masukan atau Inputnya bernilai Logika yang sama dan akan menghasilkan Keluaran (Output) Logika 0 jika semua Masukan atau Inputnya bernilai Logika yang berbeda. Hal ini merupakan kebalikan dari Gerbang X-OR (Exclusive OR).

Simbol dan Tabel Kebenaran Gerbang X-NOR (X-NOR Gate)

Flip-Flop

Pengertian Flip-Flop – Flip-flop adalah suatu rangkaian elektronika yang memiliki dua kondisi stabil dan dapat digunakan untuk menyimpan informasi. Flip Flop merupakan pengaplikasian gerbang logika yang bersifat Multivibrator Bistabil. Dikatakan Multibrator Bistabil karena kedua tingkat tegangan keluaran pada Multivibrator tersebut adalah stabil dan hanya akan mengubah situasi tingkat tegangan keluarannya saat dipicu (trigger). Flip-flop mempunyai dua Output (Keluaran) yang salah satu outputnya merupakan komplemen Output yang lain.

Jenis-jenis Flip-flop

Rangkaian Flip-flop pada umumnya dapat dibagi menjadi beberapa jenis, yaitu S-R Flip-flop, D Flip-flop, T Flip-flop dan JK Flip-flop. Berikut dibawah ini adalah penjelasan singkatnya.

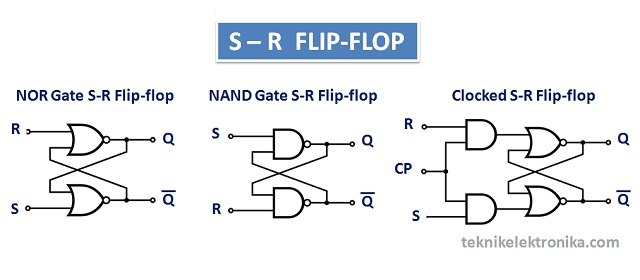

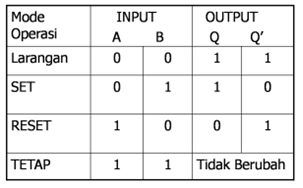

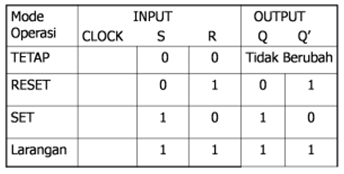

S-R Flip-flop

S-R adalah singkatan dari “Set” dan “Reset”. Sesuai dengan namanya, S-R Flip-flop ini terdiri dari dua masukan (INPUT) yaitu S dan R. S-R Flip-flop ini juga terdapat dua Keluaran (OUTPUT) yaitu Q dan Q’. Rangkaian S-R Flip-flop ini umumnya terbuat dari 2 gerbang logika NOR ataupun 2 gerbang logika NAND. Ada juga S-R Flip-flop yang terbuat dari gabungan 2 gerbang Logika NOR dan NAND.

Berikut ini adalah diagram logika NOR Gate S-R Flip-flop, NAND Gate S-R Flip-Flop dan Clocked S-R Flip-flop (gabungan gerbang logika NOR dan NAND).

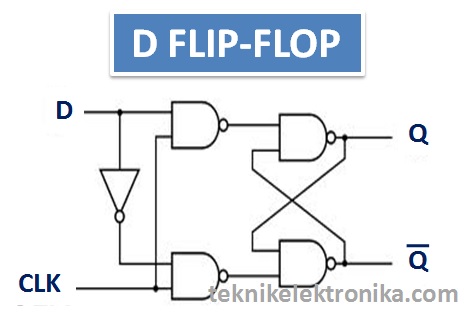

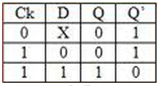

D Flip-flop

D Flip-flop pada dasarnya merupakan modifikasi dari S-R Flip-flip yaitu dengan menambahkan gerbang logika NOT (Inverter) dari Input S ke Input R. Berbeda dengan S-R Flip-flop, D Flip-flop hanya mempunyai satu Input yaitu Input atau Masukan D. Berikut ini diagram logika D Flip-flop.

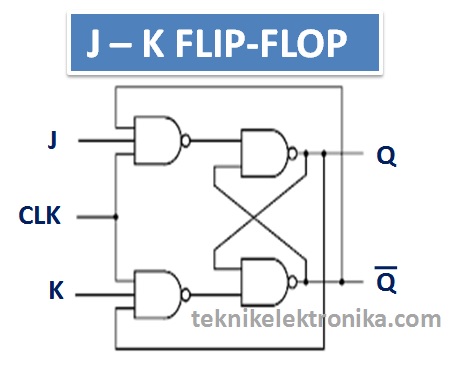

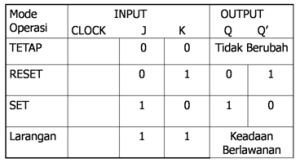

J-K Flip Flop

J-K Flip-flop juga merupakan pengembangan dari S-R Flip-flop dan paling banyak digunakan. J-K Flip-flop memiliki 3 terminal Input J, K dan CL (Clock). Berikut ini adalah diagram logika J-K Flip-flop.

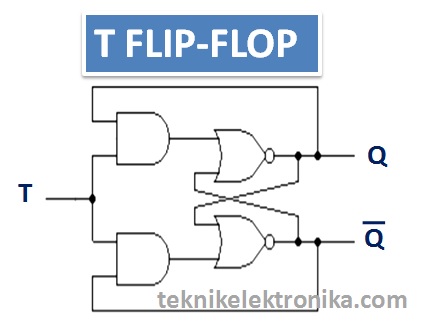

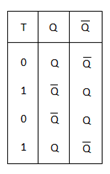

T Flip-flip

T Flip-flop merupakan bentuk sederhana dari J-K Flip-flop. Kedua Input J dan K dihubungkan sehingga sering disebut juga dengan Single J-K Flip-Flop. Berikut ini adalah diagram logika T flip-flop.

Counter

Pengertian Counter – Counter juga disebut pencacah atau penghitung yaitu rangkaian logika sekuensial yang digunakan untuk menghitung jumlah pulsa yang diberikan pada bagian masukan. Counter digunakan untuk berbagai operasi aritmatika, pembagi frekuensi, penghitung jarak (odometer), penghitung kecepatan (spedometer), yang pengembangannya digunakan luas dalam aplikasi perhitungan pada instrumen ilmiah, kontrol industri, komputer, perlengkapan komunikasi, dan sebagainya

Counter tersusun atas sederetan flip-flop yang dimanipulasi sedemikian rupa dengan menggunakan peta Karnough sehingga pulsa yang masuk dapat dihitung sesuai rancangan. Dalam perancangannya counter dapat tersusun atas semua jenis flip-flop, tergantung karakteristik masing-masing flip-flop tersebut.

Dilihat dari arah cacahan, rangkaian pencacah dibedakan atas pencacah naik (Up Counter) dan pencacah turun (Down Counter). Pencacah naik melakukan cacahan dari kecil ke arah besar, kemudian kembali ke cacahan awal secara otomatis. Pada pencacah menurun, pencacahan dari besar ke arah kecil hingga cacahan terakhir kemudian kembali ke cacahan awal.

Tiga faktor yang harus diperhatikan untuk membangun pencacah naik atau turun yaitu (1) pada transisi mana Flip-flop tersebut aktif. Transisi pulsa dari positif ke negatif atau sebaliknya,

(2) output Flip-flop yang diumpankan ke Flip-flop berikutnya diambilkan dari mana. Dari output Q atau Q,

(3) indikator hasil cacahan dinyatakan sebagai output yang mana. Output Q atau Q. ketiga faktor tersebut di atas dapat dinyatakan dalam persamaan EX-OR.

Secara global counter terbagi atas 2 jenis, yaitu: Syncronus Counter dan Asyncronous counter. Perbedaan kedua jenis counter ini adalah pada pemicuannya. Pada Syncronous counter pemicuan flip-flop dilakukan serentak (dipicu oleh satu sumber clock) susunan flip-flopnya paralel. Sedangkan pada Asyncronous counter, minimal ada salah satu flip-flop yang clock-nya dipicu oleh keluaran flip-flop lain atau dari sumber clock lain, dan susunan flip-flopnya seri. Dengan memanipulasi koneksi flip-flop berdasarkan peta karnough atau timing diagram dapat dihasilkan counter acak, shift counter (counter sebagai fungsi register) atau juga up-down counter.

1). Synchronous Counter - Syncronous counter memiliki pemicuan dari sumber clock yang sama dan susunan flip-flopnya adalah paralel. Dalam Syncronous counter ini sendiri terdapat perbedaan penempatan atau manipulasi gerbang dasarnya yang menyebabkan perbadaan waktu tunda yang di sebut carry propagation delay. Penerapan counter dalam aplikasinya adalah berupa chip IC baik IC TTL, maupun CMOS, antara lain adalah: (TTL) 7490, 7493, 74190, 74191, 74192, 74193, (CMOS) 4017,4029,4042,dan lain-lain. Pada Counter Sinkron, sumber clock diberikan pada masing-masing input Clock dari Flip-flop penyusunnya, sehingga apabila ada perubahan pulsa dari sumber, maka perubahan tersebut akan men-trigger seluruh Flip-flop secara bersama-sama.

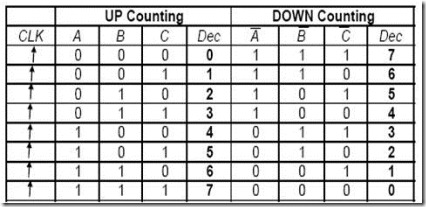

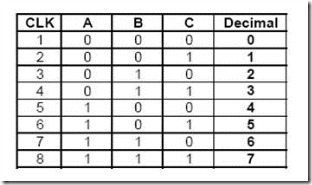

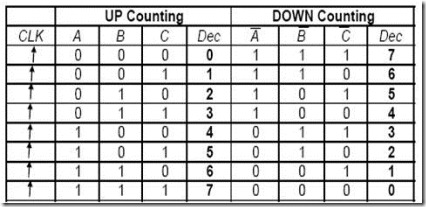

Tabel Kebenaran untuk Up Counter dan Down Counter Sinkron 3 bit :

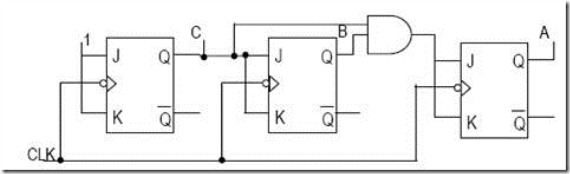

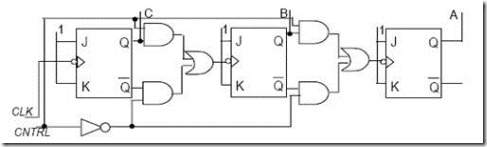

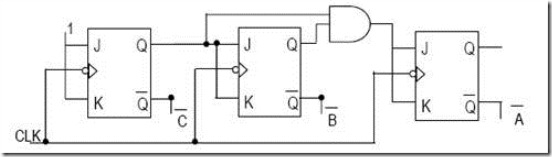

Gambar rangkaian Up Counter Sinkron 3 bit

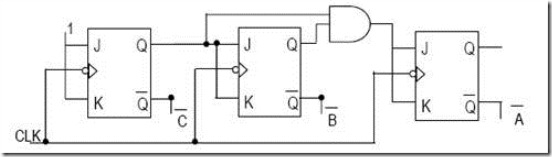

Gambar rangkaian Down Counter Sinkron 3 bit

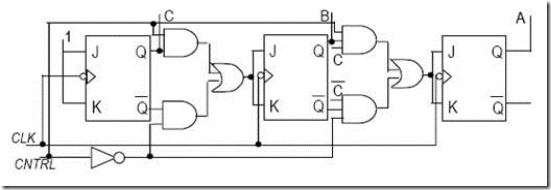

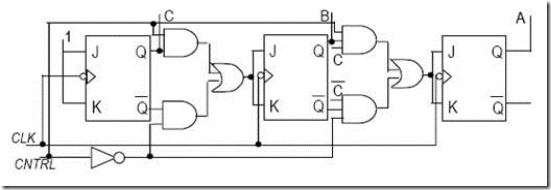

Rangkaian Up/Down Counter Sinkron

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya input eksternal sebagai control yang menentukan saat menghitung Up atau Down. Pada gambar 4.4 ditunjukkan rangkaian Up/Down Counter Sinkron 3 bit. Jika input CNTRL bernilai ‘1’ maka Counter akan menghitung naik (UP), sedangkan jika input CNTRL bernilai ‘0’, Counter akan menghitung turun (DOWN).

Gambar rangkaian Up/Down Counter Sinkron 3 bit :

2). Asyncronous counter-Asyncronous counter tersusun atas flip-flop yang dihubungkan seri dan pemicuannya tergantung dari flip-flop sebelumnya, kemudian menjalar sampai flip-flop MSB-nya. Karena itulah Asyncronous counter sering disebut juga sebagai ripple-through counter. Sebuah Counter Asinkron (Ripple) terdiri atas sederetan Flip-flop yang dikonfigurasikan dengan menyambung outputnya dari yan satu ke yang lain. Yang berikutnya sebuah sinyal yang terpasang pada input Clock FF pertama akan mengubah kedudukan outpunyanya apabila tebing (Edge) yang benar yang diperlukan terdeteksi. Output ini kemudian mentrigger inputclock berikutnya ketika terjadi tebing yang seharusnya sampai. Dengan cara ini sebuah sinyal pada inputnya akan meriplle (mentrigger input berikutnya) dari satu FF ke yang berikutnya sehingga sinyal itu mencapau ujung akhir deretan itu. Ingatlah bahwa FF T dapat membagi sinyal input dengan faktor 2 (dua). Jadi Counter dapat menghitung dari 0 sampai 2” = 1 (dengan n sama dengan banyaknya Flip-flop dalam deretan itu).

Tabel Kebenaran dari Up Counter Asinkron 3-bit

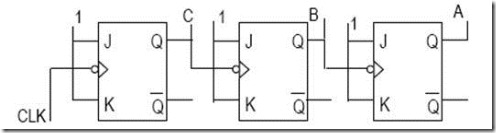

Gambar rangkaian Up Counter Asinkron 3 bit :

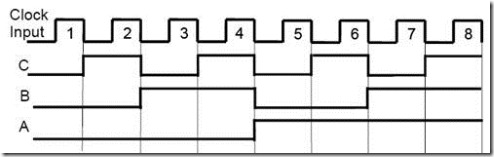

Timing Diagram untuk Up Counter Asinkron 3 bit :

Berdasarkan bentuk timing diagram di atas, output dari flip-flop C menjadi clock dari flip-flop B, sedangkan output dari flip-flop B menjadi clock dari flip-flop A. Perubahan pada negatif edge di masing-masing clock flip-flop sebelumnya menyebabkan flip-flop sesudahnya berganti kondisi (toggle), sehingga input-input J dan K di masing-masing flip-flop diberi nilai ”1” (sifat toggle dari JK flip-flop).

Counter Asinkron Mod-N-Counter Mod-N adalah Counter yang tidak 2n. Misalkan Counter Mod-6, menghitung : 0, 1, 2, 3, 4, 5. Sehingga Up Counter Mod-N akan menghitung 0 s/d N-1, sedangkan Down Counter MOD-N akan menghitung dari bilangan tertinggi sebanyak N kali ke bawah. Misalkan Down Counter MOD-9, akan menghitung : 15, 14, 13, 12, 11, 10, 9, 8, 7, 15, 14, 13,..

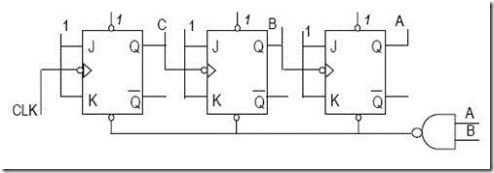

Gambar rangkaian Up Counter Asinkron Mod-6

Sebuah Up Counter Asinkron Mod-6, akan menghitung : 0,1,2,3,4,5,0,1,2,… Maka nilai yang tidak pernah dikeluarkan adalah 6. Jika hitungan menginjak ke-6, maka counter akan reset kembali ke 0. Untuk itu masing-masing Flip-flop perlu di-reset ke nilai ”0” dengan memanfaatkan input-input Asinkron-nya (

dan

). Nilai ”0” yang akan dimasukkan di PC didapatkan dengan me-NAND kan input A dan B (ABC =110 untuk desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

Gambar rangkaian Up/Down Counter Asinkron 3 bit

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya input eksternal sebagai control yang menentukan saat menghitung Up atau Down. Pada rangkaian Up/Down Counter ASinkron, output dari flip-flop sebelumnya menjadi input clock dari flip-flop berikutnya.

Perancangan Counter

Perancangan counter dapat dibagi menjadi 2, yaitu dengan menggunakan peta Karnough, dan dengan diagram waktu. Berikut ini akan dijelaskan langkah-langkah dalam merancang suatu counter.

a). Perancangan Counter Menggunakan Peta Karnaugh

Umumnya perancangan dengan peta karnaugh ini digunakan dalam merancang syncronous counter. Langkah-langkah perancangannya:

a. Dengan mengetahui urutan keluaran counter yang akan dirancang, kita tentukan masukan masing-masing flip-flop untuk setiap kondisi keluaran, dengan menggunakan tabel kebalikan.

b. Cari fungsi boolean masing-masing masukan flip-flop dengan menggunakan peta Karnough. Usahakan untuk mendapatkan fungsi yang sesederhana mungkin, agar rangkaian counter menjadi sederhana.

c. Buat rangkaian counter, dengan fungsi masukan flip-flop yang telah ditentukan. Pada umumnya digunakan gerbang-gerbang logika untuk membentuk fungsi tersebut.

b). Perancangan Counter Menggunakan Diagram Waktu

Umumnya perancangan dengan diagram waktu digunakan dalam merancang asyncronous counter, karena kita dapat mengamati dan menentukan sumber pemicuan suatu flip-flop dari flip-flop lainnya. Adapun langkah-langkah perancangannya:

1) Menggambarkan diagram waktu clock, tentukan jenis pemicuan yang digunakan, dan keluaran masing-masing flip-flop yang kita inginkan. Untuk n kondisi keluaran, terdapat njumlah pulsa clock.

2) Dengan melihat keluaran masing-masing flip-flop sebelum dan sesudah clock aktif (Qn dan Qn+1), tentukan fungsi masukan flip-flop dengan menggunakan tabel kebalikan.

3) Menggambarkan fungsi masukan tersebut pada diagram waktu yang sama.

4) Sederhanakan fungsi masukan yang telah diperoleh sebelumnya, dengan melihat kondisi logika dan kondisi keluaran flip-flop. Untuk flip-flop R-S dan J-K kondisi don’t care (x) dapat dianggap sama dengan 0 atau 1.

5) Tentukan (minimal satu) flip-flop yang dipicu oleh keluaran flip-flop lain. Hal ini dapat dilakukan dengan mengamati perubahan keluaran suatu flip-flop setiap perubahan keluaran flip-flop lain, sesuai dengan jenis pemicuannya.

6) Buat rangkaian counter, dengan fungsi masukan flip-flop yang telah ditentukan. Pada umumnya digunakan gerbang-gerbang logika untuk membentuk fungsi tersebut.